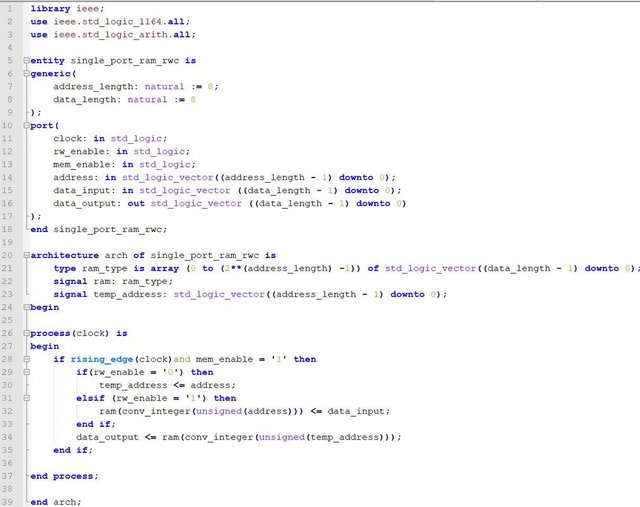

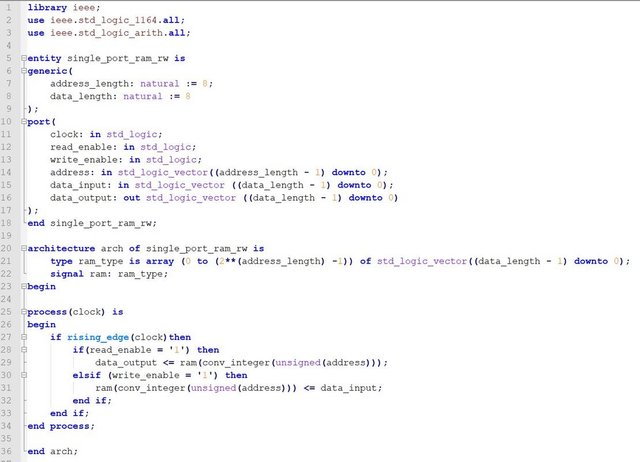

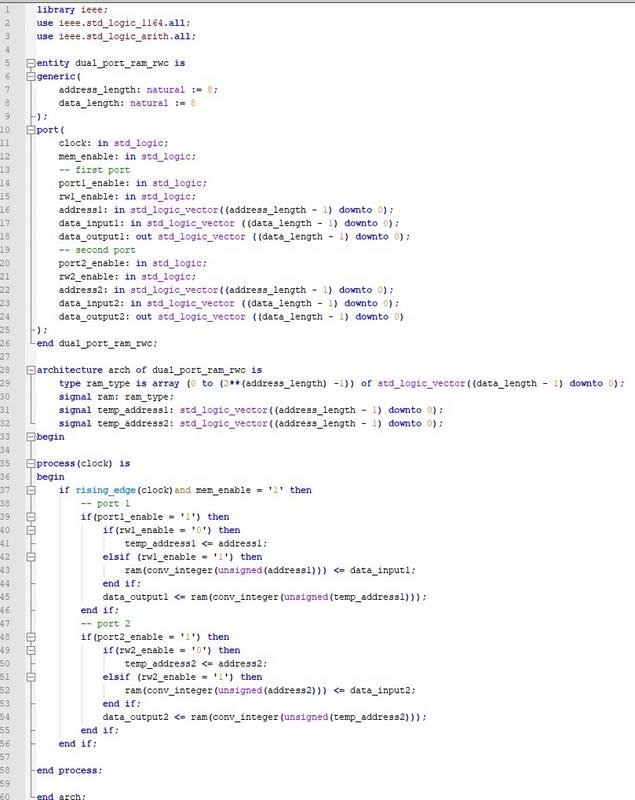

rtl - I am designing a VHDL code for memory read and write operation - Electrical Engineering Stack Exchange

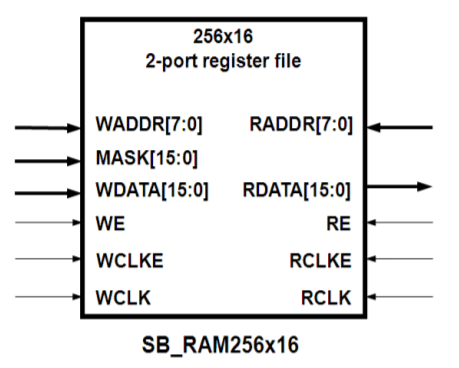

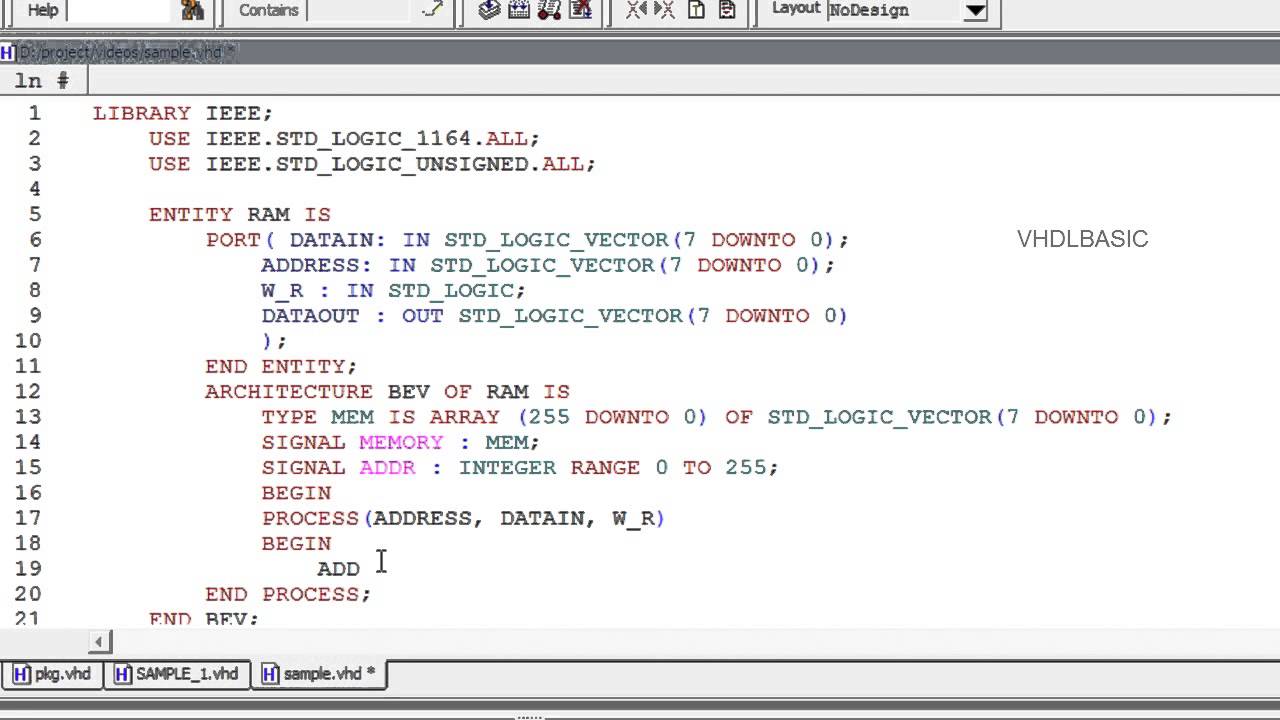

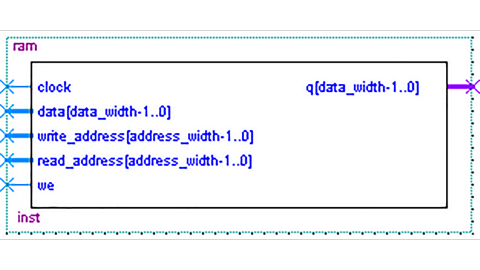

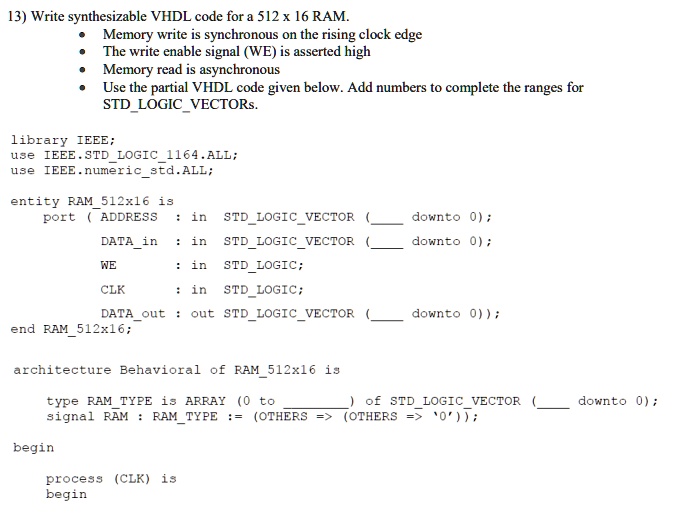

SOLVED: 13) Write synthesizable VHDL code for a 512 x 16 RAM. Memory write is synchronous on the rising clock edge. The write enable signal (WE) is asserted high. Memory read is

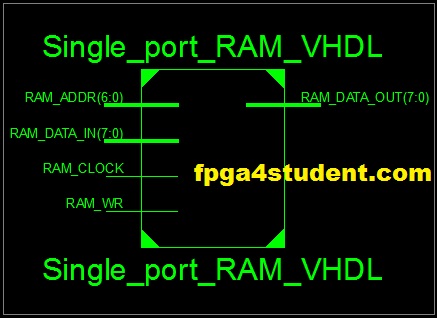

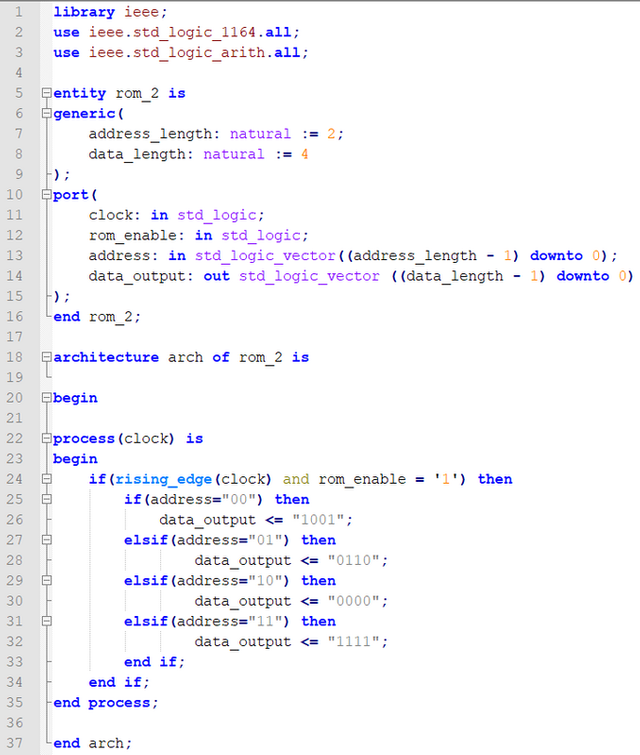

Example of a behavior description of a designed model of random-access... | Download Scientific Diagram